# 日本国特許庁 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出 願 年 月 日 Date of Application:

2002年10月21日

出 願 番 号

特願2002-306085

Application Number:

[JP2002-306085]

出 願 人

Applicant(s):

[ST. 10/C]:

株式会社デンソー

2003年 9月 1日

特許庁長官 Commissioner, Japan Patent Office 今井原

【書類名】 特許願

【整理番号】 PY20021472

【提出日】 平成14年10月21日

【あて先】 特許庁長官殿

【国際特許分類】 H03B 5/32

【発明者】

【住所又は居所】 愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

【氏名】 青山 正紀

【発明者】

【住所又は居所】 愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

【氏名】 板倉 敏和

【特許出願人】

【識別番号】 000004260

【氏名又は名称】 株式会社デンソー

【代理人】

【識別番号】 100068755

【弁理士】

【氏名又は名称】 恩田 博宣

【選任した代理人】

【識別番号】 100105957

【弁理士】

【氏名又は名称】 恩田 誠

【手数料の表示】

【予納台帳番号】 002956

【納付金額】 21,000円

【提出物件の目録】

【物件名】 明細書 1

【物件名】 図面 1

【物件名】 要約書 1

【包括委任状番号】 9908214

【プルーフの要否】 要

【書類名】 明細書

【発明の名称】 発振回路

【特許請求の範囲】

【請求項1】 能動回路  $(1 \sim 3, 71 \sim 75)$  あるいは能動素子 (80) の帰還回路として CR 回路を用いた発振回路において、

前記CR回路を構成する抵抗(5,5a,5b,81)の温度係数よりも大きな温度係数を有する抵抗(6,83,85)を、前記CR回路のコンデンサ(4,82)の充放電開始電圧および充放電時間を調整するための抵抗として組み込んだことを特徴とする発振回路。

【請求項2】 インバータを3つ以上直列に接続し、このインバータ群(1~3,71~75)のうちの奇数番目のインバータの出力端子から第1番目のインバータ(1,71)の入力端子に抵抗(5,5 a,5 b)を介して帰還をかけるとともに、少なくともいずれかのインバータの出力端子からコンデンサ(4)を介して前記第1番目のインバータ(1,71)の入力端子に帰還をかけた発振回路において、

インバータ群( $1\sim3$ ,  $71\sim75$ )のうちの偶数番目のインバータの出力端子から第1番目のインバータ(1, 71)の入力端子への前記コンデンサ(4)を介した帰還経路に、前記抵抗(5, 5a, 5b)の温度係数よりも大きな温度係数を有する抵抗(6)を配したことを特徴とする発振回路。

【請求項3】 コンパレータ(80)の一方の入力端子に対しコンデンサ(82)と抵抗(81)よりなるCR回路を介して帰還をかけるとともに、コンパレータ(80)の他方の入力端子に対し複数の抵抗(83,84,85)により分圧した電圧を印加する発振回路において、

前記分圧のための複数の抵抗(83,84,85)のうちの一部の抵抗(83,85)の温度係数を、他の分圧のための抵抗(84)および前記CR回路を構成する抵抗(81)の温度係数よりも大きなものとしたことを特徴とする発振回路。

【請求項4】 前記抵抗(5,5a,5b,6,81,83,84,85) は半導体抵抗素子である請求項1~3のいずれか1項に記載の発振回路。 【請求項5】 前記半導体抵抗素子の不純物濃度を異ならせることにより抵抗(5,5a,5b,6,81,83,84,85)の温度係数を異ならせたことを特徴とする請求項4に記載の発振回路。

【請求項6】 前記半導体抵抗素子は、不純物ドープトポリシリコン抵抗も しくは拡散抵抗であることを特徴とする請求項4または5に記載の発振回路。

【請求項7】 ワンチップ内に集積化したことを特徴とする請求項1~6のいずれか1項に記載の発振回路。

## 【発明の詳細な説明】

## [0001]

【発明の属する技術分野】

本発明は発振回路に関するものである。

#### [0002]

## 【従来の技術】

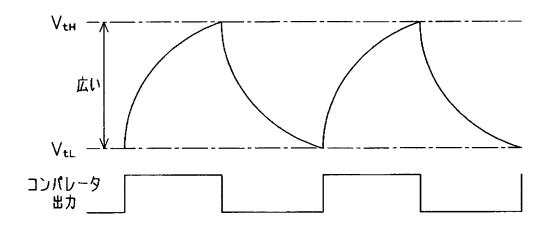

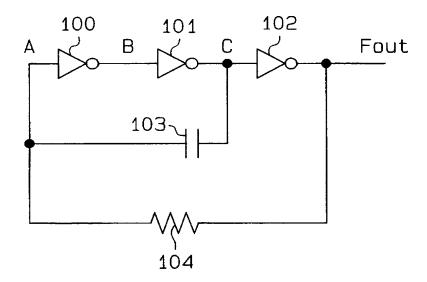

発振回路において、図18に示す回路構成とするのが一般的である。図18においてインバータ100,101,102が直列に接続され、インバータ101の出力側とインバータ100の入力側とがコンデンサ103を介して接続されている。また、インバータ102の出力側とインバータ100の入力側とが抵抗104を介して接続されている。図19において実線にて室温時におけるインバータ100の入力側(A)と、インバータ100の出力側(B)およびインバータ102の出力側(Fout)と、インバータ101の出力側(C)におけるそれぞれの波形を示す。

## [0003]

ここで、発振周波数 f 1 を決定するのは、抵抗 1 0 4 とコンデンサ 1 0 3 の充放電の時定数であり、 f 1 値は抵抗 1 0 4 での抵抗値 R 1 1 とコンデンサ 1 0 3 の容量 C 1 1 との関係において次式で表される。

#### [0004]

$f 1 = 1 / (k \cdot R 1 1 \cdot C 1 1)$

ただし、k は定数であり、約2.2の値をとる。

この場合、半導体で構成することを前提に考えると、抵抗104は拡散抵抗ま

たはポリシリコン抵抗を利用し、また、コンデンサ103は、ポリシリコン層間 膜やトランジスタのゲート酸化膜を利用したものがほとんどである。

## [0005]

ここで、発振周波数に関する温度依存性(温度特性)を考察すると、抵抗104とコンデンサ103で決定される充放電の時定数のうち抵抗104の温度依存性(温度特性)が主要因であり、その値は、拡散抵抗を用いたもので $10\sim40$ %(125  $\mathbb{C}/\mathbb{E}$  温比)、ポリシリコン抵抗を用いたもので $4\sim10$  %程度の変化量がみられる。より詳しくは、抵抗104 として温度係数の小さなものを用いるとともにコンデンサ103 として層間膜コンデンサを用いた場合において、室温時に比べ低温時および高温時には図19 で破線および一点鎖線で示すようにズレが生じ、抵抗の温度依存性(温度特性)により発振周波数が温度依存性を持つ

## [0006]

システム上、高精度な発振周波数を要求される場合においては水晶やセラロックなどの発振子を用いることが多いが、その部品代や実装代がかかるためコストアップを招いてしまう。

#### [0007]

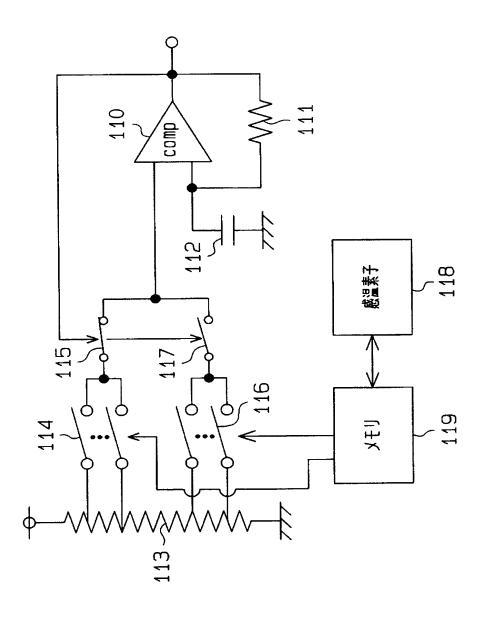

また、半導体チップ上にて周波数を一定に制御する方法として、図20のような構成がある。図20においてコンパレータ110の一方の入力端子に抵抗111とコンデンサ112よりなるCR回路を介して帰還がかけられている。一方、コンパレータ110の他方の入力端子は、抵抗113内の接続点(分圧用接続点)にスイッチ群114とスイッチ115を介して接続されるとともに、抵抗113内の接続点(分圧用接続点)にスイッチ群116とスイッチ117を介して接続されている。スイッチ115,117はコンパレータ110の出力に基づき交互にオンする。また、感温素子118とメモリ119が設けられ、感温素子118による温度測定結果に基づいてメモリ119がスイッチ群114,116のうちの所定のスイッチをオンする。つまり、スイッチ群114の中のいずれかのスイッチ、また、スイッチ群116の中のいずれかのスイッチを選択してオンする。これにより、コンパレータ110の入力端子に温度に応じた閾値電圧が印加さ

れる。つまり、感温素子118の出力と予めプログラムされたメモリ119から の信号をもとに、発振周波数を決定するコンパレータ110の閾値電圧を変化さ せて周波数を一定に制御する。

## [0008]

この場合も、制御に要する回路部分が大きくなってしまうためコストアップを 招いてしまうという問題がある。

## [0009]

#### 【発明が解決しようとする課題】

本発明はこのような背景の下になされたものであり、その目的は、簡単な構成にて、発振周波数に関する温度依存性を改善することができる発振回路を提供することにある。

## [0010]

#### 【課題を解決するための手段】

請求項1に記載の発明は、CR回路を構成する抵抗の温度係数よりも大きな温度係数を有する抵抗を、CR回路のコンデンサの充放電開始電圧および充放電時間を調整するための抵抗として組み込んだことを特徴としている。よって、CR回路を構成する抵抗の温度係数よりも大きな温度係数を有する抵抗を用いて、CR回路のコンデンサの充放電開始電圧および充放電時間が調整され、簡単な構成にて、発振周波数に関する温度依存性を改善することができるようになる。

#### $[0\ 0\ 1\ 1]$

請求項2に記載の発明は、インバータ群のうちの偶数番目のインバータの出力端子から第1番目のインバータの入力端子へのコンデンサを介した帰還経路に、奇数番目のインバータの出力端子からの帰還用抵抗の温度係数よりも大きな温度係数を有する抵抗を配したことを特徴としている。この構成によってコンデンサの充放電開始電圧および充放電時間を調整することにより、簡単な構成にて、発振周波数に関する温度依存性を改善することができる。

#### [0012]

請求項3に記載の発明は、分圧のための複数の抵抗のうちの一部の抵抗の温度係数を、他の分圧のための抵抗およびCR回路を構成する抵抗の温度係数よりも

大きなものとしたことを特徴としている。この構成によってコンデンサの充放電 開始電圧および充放電時間を調整することにより、簡単な構成にて、発振周波数 に関する温度依存性を改善することができる。

## [0013]

請求項4に記載のように、前記抵抗は半導体抵抗素子であり、請求項5に記載のように、半導体抵抗素子の不純物濃度を異ならせることにより抵抗の温度係数を異ならせることができる。また、請求項6に記載のように、半導体抵抗素子は不純物ドープトポリシリコン抵抗もしくは拡散抵抗であるとよい。

## [0014]

請求項7に記載のように、請求項1~6のいずれか1項に記載の発明において、ワンチップ内に集積化するとよい。

## [0015]

## 【発明の実施の形態】

#### (第1の実施の形態)

以下、この発明を具体化した第1の実施の形態を図面に従って説明する。

#### $[0\ 0\ 1\ 6]$

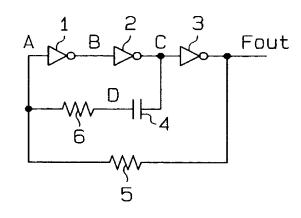

図1に、本実施形態における発振回路の構成図を示す。本実施形態における発 振回路は、ワンチップ内に集積化されている。即ち、IC化されている。

図1において、インバータ1, 2, 3が直列に接続されている。インバータ2の出力側とインバータ1の入力側との間においてコンデンサ4と抵抗6が直列に接続されている。また、インバータ3の出力側とインバータ1の入力側とが抵抗5を介して接続されている。

#### $[0\ 0\ 1\ 7]$

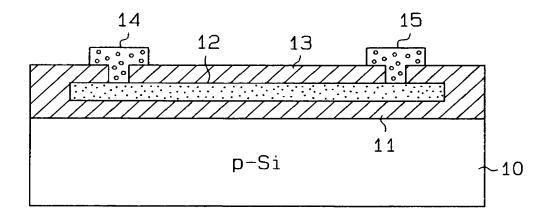

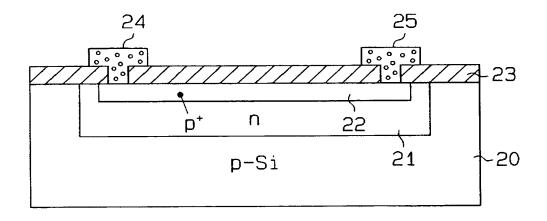

図1における抵抗5,6は、図2に示すような不純物ドープトポリシリコン抵抗あるいは図3に示すような拡散抵抗を用いている。

図2において、p型シリコン基板10の上にはシリコン酸化膜11を介して不 純物ドープトポリシリコン膜12が形成されている。不純物ドープトポリシリコ ン膜12の上にはシリコン酸化膜13を介してアルミ配線14,15が形成され ている。アルミ配線14はコンタクトホールを通して不純物ドープトポリシリコ ン膜12の一端と電気的に接続されるとともに、アルミ配線15はコンタクトホールを通して不純物ドープトポリシリコン膜12の他端と電気的に接続されている。

#### [0018]

図3において、p型シリコン基板20の表層部にはn型領域21が形成されるとともに、n型領域21の表層部にはp+領域22が形成されている。p型シリコン基板20の上にはシリコン酸化膜23を介してアルミ配線24,25が形成されている。アルミ配線24はコンタクトホールを通してp+領域22の一端側と電気的に接続されるとともに、アルミ配線25はコンタクトホールを通してp+領域22の他端側と電気的に接続されている。

#### [0019]

より具体的には、図1の抵抗5 (第1の抵抗)には、図2に示す不純物ドープトポリシリコン抵抗を使用するとともに、図1の抵抗6 (第2の抵抗)には、図3に示すp+拡散抵抗を使用している。

## [0020]

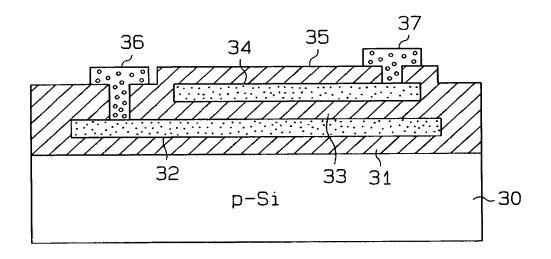

図1のコンデンサ4は、図4に示すように、ポリシリコン膜32,34の間に シリコン酸化膜33を挟んだ構造をしている。

図4において、p型シリコン基板30の上にはシリコン酸化膜31を介してポリシリコン膜32が形成されるとともに、その上にはシリコン酸化膜33を介してポリシリコン膜34が形成されている。ここで、一層目のポリシリコン膜32と二層目のポリシリコン膜34とはシリコン酸化膜33を挟んで対向して(重なるように)配置されている。ポリシリコン膜34の上にはシリコン酸化膜35を介してアルミ配線36,37が形成されている。アルミ配線36はコンタクトホールを通してポリシリコン膜34と電気的に接続されている。7はコンタクトホールを通してポリシリコン膜34と電気的に接続されている。

#### [0021]

このように、図1のコンデンサ4には、図4に示すごとく、ポリシリコン層間膜を利用している。

図1の抵抗5 (第1の抵抗) には図2に示す不純物ドープトポリシリコン抵抗

を使用するとともに図1の抵抗6 (第2の抵抗)には図3に示すp+拡散抵抗を使用したが、これに代わり次のようにしてもよい。

## [0022]

その1として、図1の抵抗5 (第1の抵抗)には図2に示す不純物ドープトポリシリコン抵抗を使用するとともに図1の抵抗6 (第2の抵抗)には図5に示す pウエル拡散抵抗を使用する。

## [0023]

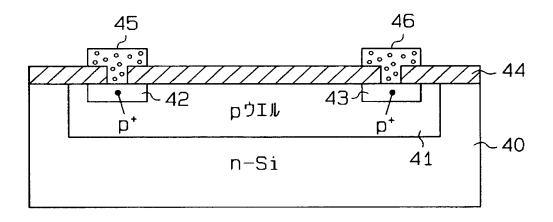

図5において、n型シリコン基板 40の表層部にはpウエル領域 41が形成されるとともに、pウエル領域 41の表層部にはp+領域 42, 43が離間して形成されている。n型シリコン基板 40の上にはシリコン酸化膜 44を介してアルミ配線 45, 46が形成されている。アルミ配線 45はコンタクトホールを通してp+領域 42と電気的に接続されるとともに、アルミ配線 46はコンタクトホールを通してp+領域 43と電気的に接続されている。

## [0024]

その2として、図1の抵抗5(第1の抵抗)には図3に示すp+拡散抵抗を使用するとともに図1の抵抗6(第2の抵抗)には図5に示すpウエル拡散抵抗を使用する。

## [0025]

また、図5に示すpウエル拡散抵抗の代わりに、図6に示すnウエル拡散抵抗を使用してもよい。

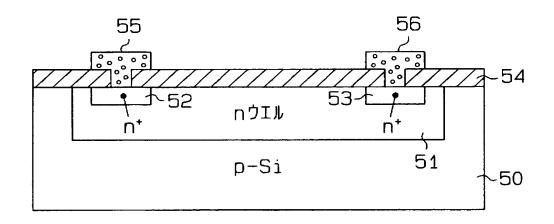

図6において、p型シリコン基板50の表層部にはnウエル領域51が形成されるとともに、nウエル領域51の表層部にはn+領域52,53が離間して形成されている。p型シリコン基板50の上にはシリコン酸化膜54を介してアルミ配線55,56が形成されている。アルミ配線55はコンタクトホールを通してn+領域52と電気的に接続されるとともに、アルミ配線56はコンタクトホールを通してn+領域53と電気的に接続されている。

#### [0026]

また、図1のコンデンサ4として、図4に示すポリシリコン膜32,34の間にシリコン酸化膜33を挟んだ構造のものを用いたが、これに代わり、図7に示

す薄膜シリコン酸化膜63を利用したものを用いてもよい。

#### [0027]

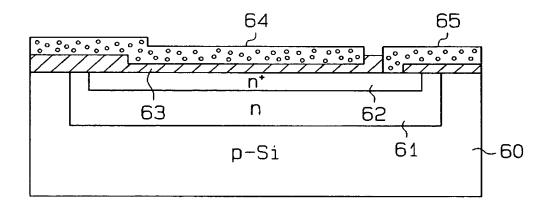

図7において、p型シリコン基板60の表層部にはn型領域61が形成されるとともに、n型領域61の表層部にはn+領域62が形成されている。p型シリコン基板60の上には薄いシリコン酸化膜63を介してアルミ配線64,65が形成されている。ここで、シリコン酸化膜63を挟んでn+領域(第1の電極材)62とアルミ配線(第2の電極材)64とが対向している。アルミ配線65はコンタクトホールを通してn+領域62と電気的に接続されている。

#### [0028]

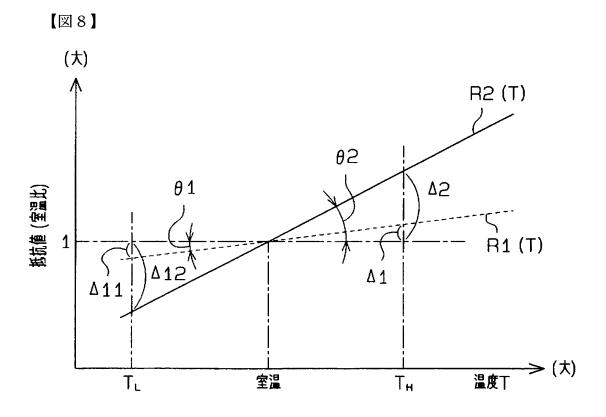

図8には、図1の第1の抵抗5の温度特性R1(T)と、図1の第2の抵抗6 の温度特性R2(T)を示す。図8において横軸には温度Tをとり、縦軸には抵 抗値をとっている。縦軸の抵抗値は室温時の値との比であり、室温では「1」と なる。

## [0029]

図8において、第1の抵抗5の温度特性R1(T)、即ち、各温度での抵抗値は破線で表し、第2の抵抗6の温度特性R2(T)、即ち、各温度での抵抗値は実線で表している。温度特性R1(T),R2(T)は共に一次関数であり、傾き $\theta$ 1, $\theta$ 2が共に正であるが、傾き $\theta$ 1, $\theta$ 2が異なっている。詳しくは、抵抗6の温度特性R2(T)における傾き(温度係数) $\theta$ 2が、抵抗5の温度特性R1(T)における傾き(温度係数) $\theta$ 2が、抵抗5の温度特性R1(T)における傾き(温度係数) $\theta$ 1よりも大きい( $\theta$ 2> $\theta$ 1)。つまり、高温時THにおいては、室温時に比べ抵抗値R1が $\Delta$ 1だけ大きいとともに、抵抗値R2が $\Delta$ 2だけ大きく、かつ $\Delta$ 2は $\Delta$ 1より大きい( $\Delta$ 2> $\Delta$ 1)。一方、低温時TLにおいては、室温時に比べ抵抗値R1が $\Delta$ 11だけ小さいとともに、抵抗値R2が $\Delta$ 12だけ小さく、かつ $\Delta$ 12は $\Delta$ 11より大きい( $\Delta$ 12> $\Delta$ 11)。

## [0030]

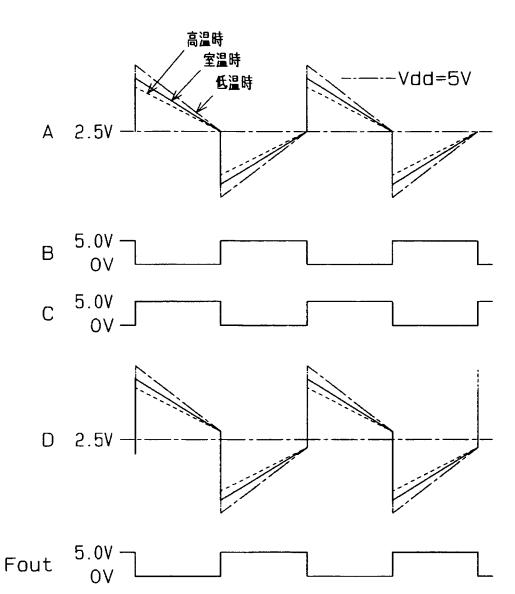

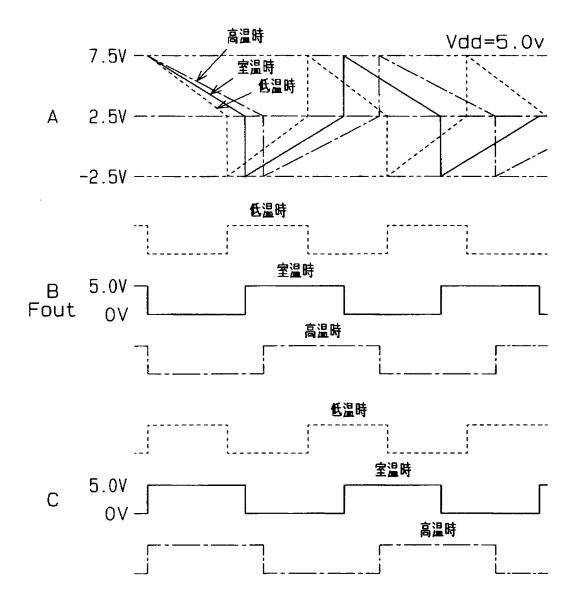

図9には、高温時、室温時、低温時における、図1のインバータ1の入力側(A)と、インバータ1の出力側(B)と、インバータ2の出力側(C)と、抵抗6・コンデンサ4間(D)と、インバータ3の出力側(Fout)におけるそれぞ

れの波形を示す。

## [0031]

インバータ1の入力側(A)での波形において、高温時、室温時、低温時において傾き(充放電時の傾き)が異なっている。これを図10の拡大図を用いて説明する。

#### [0032]

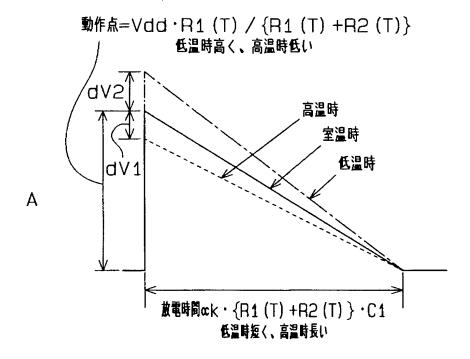

第1の抵抗5の抵抗値をR1 (T)、抵抗6の抵抗値をR2 (T)、コンデンサ4の容量をC1とする。

図10において、充放電の時定数は、

k · |R1 (T) +R2 (T) | · C1 で表される。

## [0033]

よって、充放電の時定数は、室温時に比べ低温時に小さくなり、高温時に大きくなり、充放電時間は低温時に短くなり高温時に長くなる。

また、充放電開始電圧(動作点)は、

$Vdd \cdot R 1 (T) / \{R 1 (T) + R 2 (T)\}$

で表される。ただし、V ddは駆動電圧である(② 9 の場合、V dd = 5 V ) 。

## [0034]

よって、充放電開始電圧(動作点)は、室温時に比べ低温時に高く、高温時に 低くなる。

このように、発振周波数を決定する抵抗 5, 6 での抵抗値 R 1 (T), R 2 (T) は、図 8 のように、高温時には大きくなるので、充放電の時定数は大きくなり図 1 0 に示すように充放電時間は長くなる。低温時はその逆であり、図 8 に示すように抵抗値 R 1 (T), R 2 (T) は小さくなるので、充放電の時定数は小さくなり図 1 0 に示すように充放電時間は短くなる。

## [0035]

ここで、抵抗 5,6 での抵抗値 R 1 (T), R 2 (T) が温度依存性(温度特性)を持っていても、発振周波数を一定にすべく、充放電開始電圧(動作点) および充放電時間を調整している。具体的には、不純物ドープトポリシリコン抵抗

もしくは拡散抵抗における不純物濃度を最適化してコンデンサ4の充放電開始電圧(図1における2つの抵抗5,6による分圧電圧値)および充放電時間を調整し発振周波数が一定になるようにしている。

## [0036]

即ち、不純物濃度をコントロールして、高温時においては充放電の時定数が大きくなる分だけ充放電開始電圧(動作点)を所定量(図10のdV1だけ)下げることで、発振周波数(充放電時間)を一定にする。また、低温時においては、充放電の時定数が小さくなる分だけ充放電開始電圧(動作点)を所定量(図10のdV2だけ)上げることで、発振周波数(充放電時間)を一定にする。このように、充放電時間を決定するとともに充放電開始電圧(動作点)を決定するための抵抗5,6に関して発振周波数を一定にできるような特性に調整し、発振周波数の温度特性を補償している。

#### [0037]

なお、コンデンサ4の充放電開始電圧および充放電時間の調整方法としては、 抵抗5,6として、構造の異なる抵抗を用いたり、同じ構造の抵抗を用い、かつ 、その不純物濃度を異ならせたり、構造が異なる抵抗を用い、かつ、その不純物 濃度を異ならせることにより、行うことができる。

#### [0038]

以上のように、図18に示す従来の回路構成に対し抵抗素子(図1の抵抗6)を一つ追加するのみで、温度が変化しても高精度に発振周波数を一定に保つことができ、かつ小型のため、LSI内蔵が容易にできる。つまり、図20に示すメモリ119などの大規模回路を用いずにシンプルで小型な回路構成にて発振周波数を一定に保つことができる。即ち、ICチップ上に構成される発振回路に関し、発振周波数についての温度依存性(温度特性)のうち抵抗の温度依存性(温度特性)が主要因であるので、この温度依存性(温度特性)を、メモリなどの大規模回路を用いずにシンプルで小型な回路構成にて補償することができる。

## [0039]

以上説明してきたように本実施形態は下記の特徴を有する。

- (イ)図1に示すように、能動回路(1, 2, 3)の帰還回路としてCR回路を用いた発振回路において、CR回路を構成する抵抗5の温度係数 $\theta$  1 (図8参照)よりも大きな温度係数 $\theta$  2 (> $\theta$  1)を有する抵抗6を、CR回路のコンデンサ4の充放電開始電圧および充放電時間を調整するための抵抗として組み込んだ。

- (ロ)より詳しくは、インバータ1、2、3を直列に接続し、インバータ3の出力端子からインバータ1の入力端子に抵抗5を介して帰還をかけるとともに、インバータ2の出力端子からコンデンサ4を介してインバータ1の入力端子に帰還をかけた発振回路において、インバータ2の出力端子からインバータ1の入力端子へのコンデンサ4を介した帰還経路に、抵抗5の温度係数 $\theta$ 1よりも大きな温度係数 $\theta$ 2(> $\theta$ 1)を有する抵抗6を配した。広義には、インバータを3以上直列に接続し、このインバータ群(1~3)のうちの奇数番目のインバータの出力端子から第1番目のインバータ1の入力端子に抵抗5を介して帰還をかけるとともに、少なくともいずれかのインバータの出力端子からコンデンサ4を介して第1番目のインバータ1の入力端子に帰還をかけた発振回路において、インバータ群(1~3)のうちの偶数番目のインバータの出力端子から第1番目のインバータの出力端子から第1番目のインバータの出力端子から第1番目のインバータがよび高速に表いて、インバータ群(1~3)のうちの偶数番目のインバータの出力端子から第1番目のインバータがよりまする振振6を配した。

#### $[0\ 0\ 4\ 0\ ]$

よって、(イ)においては、CR回路を構成する抵抗5の温度係数よりも大きな温度係数を有する抵抗6を用いて、CR回路のコンデンサ4の充放電開始電圧および充放電時間が調整され、簡単な構成にて、発振周波数に関する温度依存性を改善することができる。(ロ)の構成によってコンデンサ4の充放電開始電圧および充放電時間を調整することにより、簡単な構成にて、発振周波数に関する温度依存性を改善することができる。

(ハ)より具体的には、抵抗5,6は半導体抵抗素子であり、半導体抵抗素子の不純物濃度を異ならせることにより抵抗5,6の温度係数を異ならせることができる。また、半導体抵抗素子は、不純物ドープトポリシリコン抵抗もしくは拡散抵抗を用いるとよい。

## [0041]

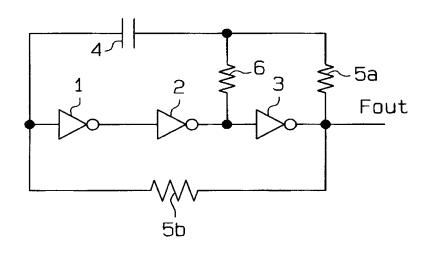

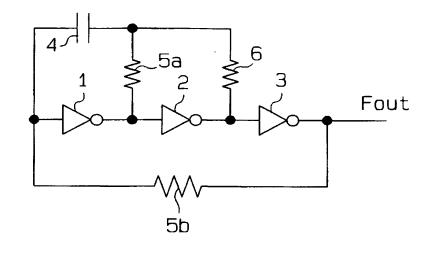

図1に代わる構成として、図11,12,13,14に示す構成としてもよい、

図11において、3つのインバータ1,2,3を直列に接続し、第3番目のインバータ3の出力端子から第1番目のインバータ1の入力端子に抵抗5aおよびコンデンサ4を介して帰還をかけるとともに、インバータ3の出力端子からインバータ1の入力端子に抵抗5bを介して帰還をかけている。また、第2番目のインバータ2の出力端子から第1番目のインバータ1の入力端子へのコンデンサ4を介した帰還経路に、抵抗5a,5bの温度係数よりも大きな温度係数を有する抵抗6を配している。

#### [0042]

図12の回路は図11の回路と等価である。図12において、3つのインバータ1,2,3を直列に接続し、第1番目のインバータ1の出力端子から第1番目のインバータ1の入力端子に抵抗5aおよびコンデンサ4を介して帰還をかけるとともに、第3番目のインバータ3の出力端子からインバータ1の入力端子に抵抗5bを介して帰還をかけている。また、第2番目のインバータ2の出力端子から第1番目のインバータ1の入力端子へのコンデンサ4を介した帰還経路に、抵抗5a,5bの温度係数よりも大きな温度係数を有する抵抗6を配している。

#### [0043]

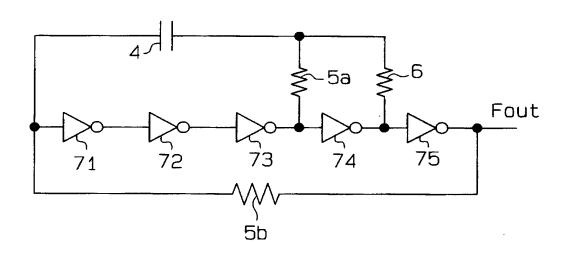

図13において、5つのインバータ71,72,73,74,75を直列に接続し、第3番目のインバータ73の出力端子から第1番目のインバータ71の入力端子に抵抗5aおよびコンデンサ4を介して帰還をかけている。また、第5番目のインバータ75の出力端子からインバータ71の入力端子に抵抗5bを介して帰還をかけている。さらに、第4番目のインバータ74の出力端子から第1番目のインバータ71の入力端子へのコンデンサ4を介した帰還経路に、抵抗5a,5bの温度係数よりも大きな温度係数を有する抵抗6を配している。

#### [0044]

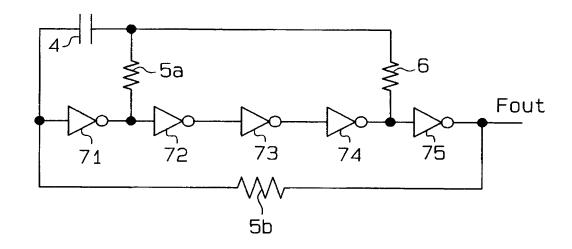

図14において、5つのインバータ71,72,73,74,75を直列に接続し、第1番目のインバータ71の出力端子から第1番目のインバータ71の入

力端子に抵抗5 a およびコンデンサ4を介して帰還をかけている。また、第5番目のインバータ75の出力端子からインバータ71の入力端子に抵抗5 b を介して帰還をかけている。さらに、第4番目のインバータ74の出力端子から第1番目のインバータ71の入力端子へのコンデンサ4を介した帰還経路に、抵抗5 a , 5 b の温度係数よりも大きな温度係数を有する抵抗6を配している。

## (第2の実施の形態)

次に、第2の実施の形態を説明する。

#### [0045]

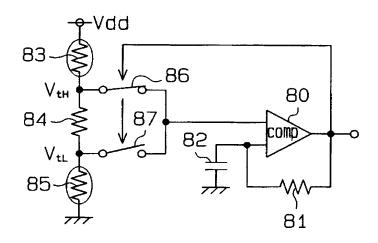

図15に、本実施形態における発振回路の構成図を示す。本実施形態における 発振回路もワンチップ内に集積化されている。即ち、IC化されている。

図15において、能動素子としてのコンパレータ80を具備している。また、抵抗81とコンデンサ82を帰還回路として用いている。この帰還回路(CR回路)にてコンパレータ80の一方の入力端子(第1の入力端子)に帰還がかけられている。また、電源端子(Vdd)とグランド間において3つの抵抗83,84,85が直列に接続されている。抵抗83と抵抗84との間がスイッチ86を介してコンパレータ80の他方の入力端子(第2の入力端子)と接続されている。そして、抵抗83と抵抗84との間の電位にて高圧側の閾値電圧VtHが規定される。また、抵抗84と抵抗85との間がスイッチ87を介してコンパレータ80の他方の入力端子(第2の入力端子)と接続されている。そして、抵抗84と抵抗85との間の電位にて低圧側の閾値電圧VtLが規定される。このようにして、コンパレータ80の他方の入力端子(第2の入力端子)に3つの抵抗83,84,85により分圧した電圧が印加される。また、コンパレータ80の出力によりスイッチ86,87が交互にオンされ、コンパレータ80の入力端子(第2の入力端子)に高圧側閾値電圧VtHと低圧側閾値電圧VtLが交互に印加される。

#### [0046]

ここで、抵抗83,85の温度係数を、抵抗84およびCR回路を構成する抵抗81の温度係数よりも大きくしている。詳しくは、抵抗83,84,85,8 1は、図2に示したような不純物ドープトポリシリコン抵抗もしくは図3,5,6で示したような拡散抵抗であり、抵抗83,85の不純物濃度を、抵抗84お よび抵抗81の不純物濃度と異ならせることにより、抵抗83,85の温度係数を、抵抗84および抵抗81の温度係数よりも大きくしている。

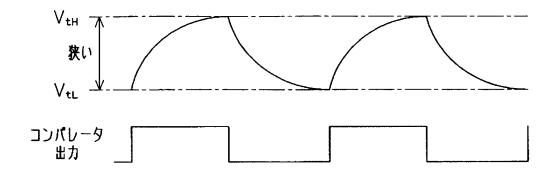

#### [0047]

これにより、図16に示す高温時においては高圧側閾値電圧VtHと低圧側閾値電圧VtLの幅を狭くし、図17に示す低温時においては高圧側閾値電圧VtHと低圧側閾値電圧VtLの幅を広くし、発振周波数(充放電時間)を一定に制御している。このようにして、図15のコンデンサ82による充放電動作時の充放電時間および充放電開始電圧を調整している。

#### [0048]

なお、コンデンサ82の充放電開始電圧および充放電時間の調整方法としては 、抵抗81,83,84,85として、構造の異なる抵抗を用いたり、同じ構造 の抵抗を用い、かつ、その不純物濃度を異ならせたり、構造が異なる抵抗を用い 、かつ、その不純物濃度を異ならせることにより、行うことができる。

## [0049]

このように、図20の改良型として、感温素子118やメモリ119を必要とせず、小型で、温度が変化しても発振周波数を一定に保つことができる。

以上説明してきたように本実施形態は下記の特徴を有する。

- (イ)図15に示すように、能動素子としてのコンパレータ80の帰還回路としてCR回路を用いた発振回路において、CR回路を構成する抵抗81の温度係数よりも大きな温度係数を有する抵抗83,85を、CR回路のコンデンサ82の充放電開始電圧(VtH,VtL)および充放電時間を調整するための抵抗として組み込んだ。

- (ロ)より詳しくは、コンパレータ80の一方の入力端子に対しコンデンサ82と抵抗81よりなるCR回路を介して帰還をかけるとともに、コンパレータ80の他方の入力端子に対し複数の抵抗83,84,85により分圧した電圧を印加する発振回路において、分圧のための複数の抵抗83,84,85のうちの一部の抵抗83,85の温度係数を、他の分圧のための抵抗84およびCR回路を構成する抵抗81の温度係数よりも大きなものとした。

## [0050]

よって、(イ)においては、CR回路を構成する抵抗81の温度係数よりも大きな温度係数を有する抵抗83,85を用いて、CR回路のコンデンサ82の充放電開始電圧および充放電時間が調整され、簡単な構成にて、発振周波数に関する温度依存性を改善することができる。(ロ)の構成によってコンデンサ82の充放電開始電圧および充放電時間を調整することにより、簡単な構成にて、発振周波数に関する温度依存性を改善することができる。

## [0051]

本実施形態においても、抵抗81,83,84,85は半導体抵抗素子であり、半導体抵抗素子の不純物濃度を異ならせることにより抵抗81,84と抵抗83,85の温度係数を異ならせることができる。また、半導体抵抗素子は、不純物ドープトポリシリコン抵抗もしくは拡散抵抗を用いるとよい。

#### 【図面の簡単な説明】

- 【図1】第1の実施の形態における発振回路の構成図。

- 【図2】不純物ドープトポリシリコン抵抗を示す縦断面図。

- 【図3】 p +拡散抵抗を示す縦断面図。

- 【図4】 コンデンサを示す縦断面図。

- 【図5】 p ウエル拡散抵抗を示す縦断面図。

- 【図6】nウエル拡散抵抗を示す縦断面図。

- 【図7】コンデンサを示す縦断面図。

- 【図8】温度特性を示す図。

- 【図9】各部位での波形を示す図。

- 【図10】波形の一部を拡大した図。

- 【図11】別例の発振回路の構成図。

- 【図12】別例の発振回路の構成図。

- 【図13】別例の発振回路の構成図。

- 【図14】別例の発振回路の構成図。

- 【図15】第2の実施の形態における発振回路の構成図。

- 【図16】波形を示す図。

- 【図17】波形を示す図。

- 【図18】従来技術を説明するための発振回路の構成図。

- 【図19】各部位での波形を示す図。

- 【図20】従来技術を説明するための発振回路の構成図。

## 【符号の説明】

1 …インバータ、2 …インバータ、3 …インバータ、4 …コンデンサ、5 …抵抗、5 a …抵抗、5 b …抵抗、6 …抵抗、7 1 …インバータ、7 2 …インバータ、7 3 …インバータ、7 4 …インバータ、7 5 …インバータ、8 0 …コンパレータ、8 1 …抵抗、8 2 …コンデンサ、8 3 …抵抗、8 4 …抵抗、8 5 …抵抗。

【書類名】

図面

【図1】

5 - 第1の抵抗 (抵抗値R1) = 温度係数: 小6 - 第2の抵抗 (抵抗値R2) = 温度係数: 大

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

## <高温時>

# 【図17】

# <低温時>

【図18】

【図19】

【図20】

【書類名】 要約書

【要約】

【課題】簡単な構成にて、発振周波数に関する温度依存性を改善することができる発振回路を提供する。

【解決手段】インバータ1,2,3が直列に接続され、インバータ3の出力端子からインバータ1の入力端子に抵抗5を介して帰還がかけるとともに、インバータ2の出力端子からコンデンサ4を介してインバータ1の入力端子に帰還がかけられている。インバータ2の出力端子からインバータ1の入力端子へのコンデンサ4を介した帰還経路に、抵抗5の温度係数よりも大きな温度係数を有する抵抗6が配置され、コンデンサ4の充放電開始電圧および充放電時間を調整している

【選択図】 図1

## 特願2002-306085

## 出願人履歴情報

識別番号

[000004260]

1. 変更年月日 [変更理由]

1996年10月 8日 名称変更

住 所

愛知県刈谷市昭和町1丁目1番地

氏 名 株式会社デンソー